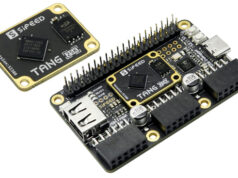

Con un módulo de conectividad Wi-Fi+Bluetooth, la placa iCE40 Wireless ofrece grandes facilidades para la programación y el debugado.

Lattice Semiconductor añade un nuevo ejemplar a su serie de placas iCE40, la cual incluye conectividad sin hilos.

La placa iCE40 Wireless se está financiando a través de una campaña de micromecenazgo (crowdfunding), y se basa en la FPGA SG48 de la misma Lattice Semi, la cual dispone de 5.280 LUTs, una RAM EBR de 120 Kbits, y una memoria PSRAM de 1.024 Kbits. Como memoria RAM externa, dispone de 8 MB de PSRAM.

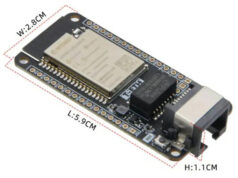

Las capacidades inalámbricas pasan por un módulo ESP32-C3-MINI-1 que dispone de Wi-Fi operando en la banda de los 2,4 GHz (Wi-Fi 4), y Bluetooth compatible con bajo consumo (BLE). Este módulo se basa en un procesador RISC-V ESP32-C3, y cuenta con 4 MB de memoria flash.

La iCE40 Wireless cuenta con un puerto USB de tipo C, que le sirve tanto para la alimentación, como para su programación, y el debugado JTAG del módulo ESP32-C3.

Su capacidad de expansión pasa por tres conectores PMOD conectados a la FPGA, un conector de E/S con siete líneas GPIO de la ESP32-C3 (serie, ADC, I2X), y una línea FPGA, además de alimentación, toma de tierra y reset.

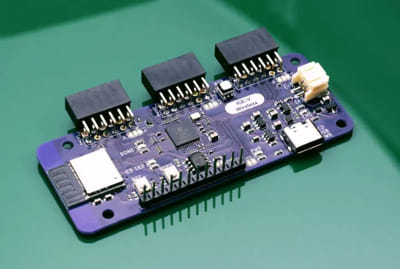

Otras funcionalidades en la placa

También cuenta con indicadores LED RGB, botones de reset y arranque, y varios indicadores LED para funcionamiento y alimentación entre otros. Funciona con un suministro de 5 V mediante un puerto USB-C y dispone de un cargador para montarle una batería LiPo.

Su diseño ha corrido a cargo de QWERTY Embedded Design, y su firmware se encuentra disponible en forma de código abierto y está escrito en lenguaje C mediante la toolchain ESP-IDF v. 5.0 y sus correspondientes librerías, y proporciona una interfaz de socket TCP sobre Wi-Fi que es capaz de cargar la configuración de la FPGA en el momento del arranque, procedente de un sistema de ficheros SPIFFS contenido en una memoria flash del ESP32-C3, además de permitir las actualizaciones de la FPGA sobre Wi-Fi (con la ESP32 y la iCE40 conectadas a través de SPI), y de monitorizar el voltaje de la batería LiPo.