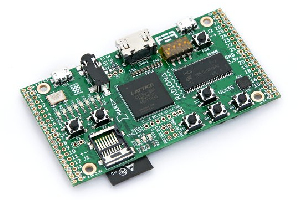

Con un bajo consumo en modo standby, esta placa FPGA para desarrolladores puede llevar conectada directamente una pantalla de pequeño tamaño.

La ULX3S es un proyecto que pronto llegará a la plataforma de micro mecenazgo Crowd Supply y cuyo objetivo es el de construir una placa FPGA con la comunidad de desarrolladores en mente.

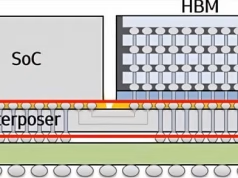

Desarrollado desde 2016 años por Radiona.org, Zagreb Makerspace y la facultad de ingenieros eléctricos y computación de Zagreb, esta placa tiene unas dimensiones de 94×51 mm, y está equipada con una FPGA Lattice ECP5, dando lugar a cuatro modelos distintos: LFE5U-85F-6BG381C (84 K LUT), LFE5U-45F-6BG381C (44 K LUT), LFE5U-25F-6BG381C (24 K LUT), y LFE5U-12F-6BG381C (12 K LUT).

Al procesador lo acompañan 32 MB de memoria SDRAM funcionando a 166 MHz. Como almacenamiento interno cuenta con una Flash Quad-SPI de entre 4 y 16 MB que permite almacenar la configuración de la FPGA y los datos de usuario, a lo cual hay que añadir un slot microSD.

La conexión USB está gestionada por un FTDI FT231XS (JTAG de 500 kbit, y USB-serial de 3 Mbit). Cuenta con GPIO de 56 pines contando 28 pares diferentes), PMOD-friendly con salida de potencia de 3,3 V a 1 A, o 2,5 V a 1,5 A.

Por otro lado, esta placa FPGA para desarrolladores cuenta con siete botones, siendo cuatro de ellos de dirección, dos de activación, y uno de alimentación. También dispone de once indicadores LED, ocho de ellos a ser definidos por el usuario, dos correspondientes a USB, y uno para el Wi-Fi.

Conectividad en la tarjeta de desarrollo

Tanto la conectividad inalámbrica Wi-Fi como la Bluetooth se solventan con un placeholder para ESP32 (interfaz web JTAG standalone sobre Wi-Fi), con antena FM/ASK en placa con soporte para las frecuencias de 27, 88-108, 14 y 433 MHz.

Cuenta con un jack de audio de 3,5 mm y cuatro contactos (estéreo analógico más audio digital, o vídeo compuesto), y una interfaz GPDI (General-Purpose Differential Interface) con un I²C variador de nivel direccional de 3,3 a 5 V.

Para el display, disponemos de un placeholder para una pantalla OLED SSD1331 SPI a color de 0,96 pulgadas. El ADC es un MAX11125 de ocho canales, 12 bits, y 1 MS a/s. En modo standby consume 5 µA a 5 V.

Hay más información técnica sobre esta placa FPGA para desarrolladores en https://www.crowdsupply.com/radiona/ulx3s