Consideraciones sobre la omisión del procesador GenAI

Los condensadores de desacoplamiento necesarios para soportar un procesador de entrenamiento genAI deben estar ubicados lo más cerca posible de las micro bolas de alimentación y tierra del complejo paquete de chiplets, y así competir con los VR por el área de PCB disponible.

La capacitancia de derivación requerida se relaciona con la tolerancia de ondulación de la fuente de alimentación del riel del procesador, la respuesta de frecuencia del subsistema de regulación de voltaje y varios otros factores. (6)

Como era de esperar, un procesador de entrenamiento genAI de corriente de diseño térmico (TDC o consumo continuo) de 1.000 Amperios requiere una gran cantidad de capacitancia de derivación, 3 mF o más, que generalmente ocupa toda el área de PCB debajo del procesador, dejando poco espacio para la colocación de VR dentro de la matriz de componentes del condensador.

Con una densidad de corriente VR de 1 A / mm2, que es el estado actual de la técnica, es posible instalar un módulo de potencia capaz de 350 Amperios (continuos) en un área de 3.500 mm2 entre los condensadores de derivación, y aun así, lograr el rendimiento dI / dt requerido.

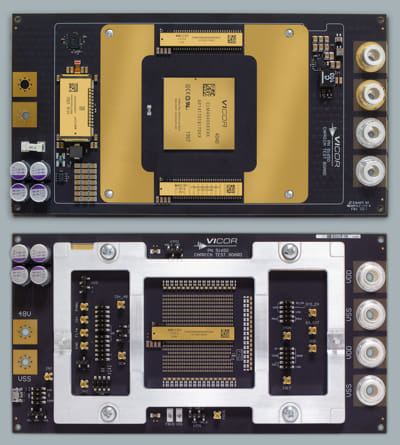

Para evaluar el rendimiento de este método de colocación de realidad virtual, se desarrolló una placa de pruebas (Figura 4) que permite medir la mejora de la pérdida térmica que ofrece la entrega de energía LVD a un procesador VDD de núcleo de 1.000 Amperios, en comparación con una ubicación de módulo lateral pura.

El módulo colocado verticalmente en la parte inferior comparte la función de suministro de corriente del riel principal del procesador con otros dos módulos de 350 Amperios (continuos) con la misma huella, que entregan energía lateralmente en la parte superior de la placa, como se muestra en la Figura 4.

Se encontró que el enfoque de diseño lateral-vertical tiene ventajas significativas sobre un diseño lateral puro.

Una nota importante: la placa de pruebas se diseñó con un módulo de carga y no con un procesador real, donde se debería tener en cuenta el enrutamiento de señal de alta velocidad (como los carriles serie basados en SERDES) y otras consideraciones en el diseño de la placa de circuito impreso PCB.

Los resultados de las pruebas muestran que la migración de uno de los módulos de alimentación VDD PoL principales de la ubicación lateral a la vertical debajo del procesador redujo la impedancia de PDN en un factor de seis.

La impedancia de PDN agrupada en paralelo se redujo de 60 a 11 en total para los tres módulos de potencia utilizados para suministrar los 1.000 Amperios continuos completos, y la disipación de PCB cayó de 60 vatios en la entrega de potencia lateral a 11 vatios en la entrega de potencia lateral-vertical.

Se trata de una reducción de 50 W/PCB a 1.000 Amperios de corriente de carga por módulo acelerador, y de 3.200 W/PCB continuos para un rack de centro de datos con procesador genAI compuesto por 64 AM.

Utilizando las previsiones de demanda de dominio público de los módulos aceleradores de genAI en los próximos años (más de 2,5 millones de unidades en 2024) (9) (10) (11) y utilizando estimaciones razonables a futuro del coste de la energía eléctrica (30 dólares por megavatio-hora), este ahorro de 50 vatios por AM conduce, para 2027, a un ahorro de teravatios-hora de energía a nivel de centro de datos mundial, equivalente a miles de millones de dólares en costos operativos eléctricos, más millones de toneladas de reducciones de emisiones de dióxido de carbono (dependiendo de la combinación de energía renovable) anualmente y a perpetuidad.