Modelado de pérdida de potencia de PCB

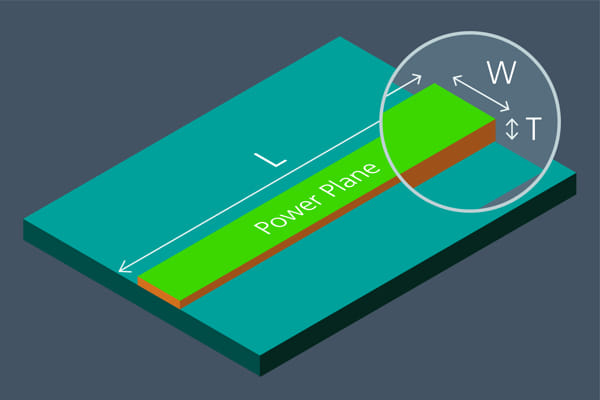

La resistencia de la placa de circuito impreso (PCB) es proporcional a la resistividad del cobre, el área y el grosor del plano de potencia y la temperatura.

La resistencia del plano de potencia de PCB de cobre se modela conceptualmente mediante la ecuación:

R = [(ρ • L) / (T • W)] • [1 + a • (temperatura ambiente Celsius – 25 °C)]

Dónde:

ρ = resistividad de cobre (1,7 x 10-6 ohmios-cm)

L = longitud del avión (cm)

W = anchura del plano (cm)

T = espesor del plano (cm)

a = coeficiente de temperatura del cobre (3,9 x 10-3/°C)

Como se puede observar en esta ecuación, la resistencia del plano de potencia es linealmente proporcional al área de la sección transversal del plano. (5) Al reubicar los convertidores PoL más cerca del procesador de entrenamiento genAI, se puede reducir el área del plano de potencia y la resistencia de CC de la red de suministro de energía (PDN).

Los diseñadores de sistemas de alimentación del procesador GenAI reconocen cada vez más la importancia crítica del área del plano de alimentación de PCB como un medio importante para reducir las pérdidas generales de energía del módulo acelerador (AM). Como resultado, buscan mejoras de ingeniería en la densidad de corriente y un mejor empaquetado del módulo de alimentación PoL VR para permitir la colocación más cerca de los pines de alimentación del procesador.

Opciones de ubicación del módulo de alimentación para procesadores GenAI

La administración de energía PoL del procesador de entrenamiento GenAI es compleja, con múltiples dominios de energía, incluido el riel principal (VDD central) de tan solo 0,7 voltios, solo capaz de tolerar sobreimpulsos y subimpulsos de ± 5% más o menos.

El consumo de corriente está impulsado por la carga de trabajo del algoritmo (es decir, depende de la tarea del software), lo que da como resultado niveles extremadamente altos de tasa de cambio de tiempo de corriente (dI/dt) de 2.000 Amperios por microsegundo o más. Este alto rango dinámico requiere que la solución de suministro de energía PoL tenga una capacidad de corriente máxima (por lo general, de 1 a 2 ms de duración) de aproximadamente el doble del nivel de corriente continua de CC.

Los HBM del conjunto de procesadores tienen su propio dominio de tensión (HBM VDD) a 1,1 o 1,2 V nominal, y también tienen limitaciones en cuanto a los requisitos de corriente continua y máxima, dI/dt y límites de tensión transitoria por encima y por debajo de la tensión nominal de funcionamiento, para evitar daños en el circuito o degradación de la vida útil. También hay dominios de voltaje auxiliar (VDD auxiliar) en la matriz del procesador con requisitos de corriente de aproximadamente 250 a 400 Amperios.

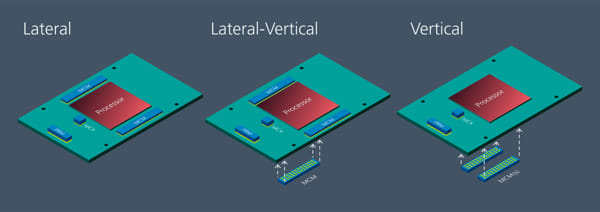

La Figura 3 muestra tres opciones de ubicación del módulo de potencia para la entrega de energía VR, lateral (LPD), lateral-vertical (LVD) y vertical (VPD).

La colocación de VR directamente debajo del procesador, como con las opciones LVD y VPD, reduce la resistencia de PDN. Esto minimiza el área del plano de potencia con las ventajas que se han comentado, pero normalmente es donde se encuentra la gran gama de condensadores de derivación, lo que proporciona una derivación de gran ancho de banda y un suministro de corriente transitoria para cargas de trabajo dinámicas de genAI.