Los nuevos encapsulados TSC QDPAK y DDPAK aportan mejoras considerables en el diseño de cargadores OBC y conversión DC-DC.

Las tendencias hacia una mayor densidad de potencia y una optimización de coste dominan los objetivos de desarrollo en aplicaciones de alta potencia que crean valor añadido en segmentos como la electromovilidad.

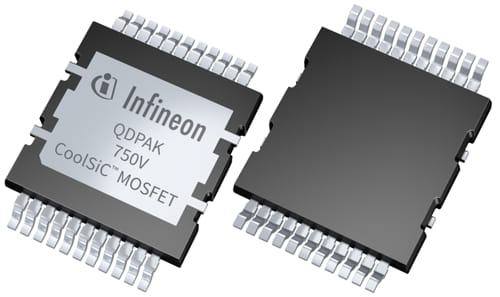

Con el objetivo de respaldar estos avances, Infineon Technologies anuncia que ha registrado sus encapsulados de refrigeración en la parte superior (top-side cooling – TSC) QDPAK y DDPAK, ideales para MOSFET de elevada tensión como un estándar JEDEC.

Este registro fortalece el compromiso de Infineon de ayudar en la adopción de TSC en nuevos diseños con un encapsulado estándar. Además, ofrece flexibilidad y comodidad a los OEM para diferenciar sus productos y llevar la densidad de potencia al siguiente nivel y así soportar diversas aplicaciones.

Desde hace más de medio siglo, la asociación JEDEC desarrolla estándares abiertos y publicaciones para la industria de la microelectrónica y una amplia variedad de tecnologías, incluyendo los esquemas de encapsulado. JEDEC ha aceptado encapsulados como dispositivos through–hole (THD) TO220 y TO247, empleados durante las pasadas décadas y todavía una opción en los nuevos diseños de cargadores (OBC) y convertidores DC-DC de alta y baja tensión (HV y LV).

El registro de diseños de encapsulado TSC de montaje superficial (SMD) QDPAK y DDPAK “inicia una nueva era en los esquemas de encapsulado para guiar la adopción de la tecnología TSC como sustituta de TO247 y TO220, respectivamente”.

Gracias a los beneficios de esta tecnología, el registro de esta nueva familia de encapsulado JEDEC, de acuerdo al estándar MO-354, sirve como un “impulsor” en la transición de aplicaciones industriales y de automoción de alta tensión a diseños top–side cooled en plataformas de próxima generación.

Facilidades para mejorar los diseños electrónicos

Para facilitar la transición de los clientes desde dispositivos THD TO220 y TO247, Infineon ha presentado los dispositivos SMD QDPAK y DDPAK para garantizar unas capacidades térmicas equivalentes con mejoras en rendimiento eléctrico. Basándose en una altura estándar de 2,3 mm para encapsulado TSC SMD QDPAK y DDPAK en dispositivos HV y LV, los desarrolladores pueden diseñar aplicaciones completas, como OBC y conversión DC-DC, con todos los dispositivos TSC SMD teniendo la misma altura. En comparación con las soluciones existentes que requieren un sistema de refrigeración 3D, esto simplifica los diseños y reduce los costes de refrigeración de sistema.

Además, el encapsulado TSC ofrece una resistencia térmica hasta un 35 por ciento menor que modelos bottom–side cooling (BSC) estándares. Al permitir el uso de ambos lados de PCB, los encapsulados TSC proporcionan una mejor utilización del espacio de tarjeta y, al menos, doblar la densidad de potencia. La gestión térmica también mejora por el desacople térmico del sustrato, ya que la resistencia térmica de las cargas es mucho mayor. Y, como consecuencia del aumento del rendimiento térmico, ya no resulta necesario el apilado de diferentes tarjetas. En lugar de combinar FR4 e IMS, un solo FR4 es suficiente para todos los componentes y también se requieren menos conectores. Esta reducción en la lista de materiales (BOM) disminuye el coste total del sistema.

Aparte de mejorar las capacidades térmicas y de alimentación, la tecnología TSC ofrece un diseño de bucle de alimentación optimizado para incrementar la fiabilidad. Esto es posible por la ubicación de los controladores, que se pueden posicionar muy cerca del interruptor de alimentación. La baja inductancia parásita del bucle del interruptor del controlador reduce los parásitos del bucle y conduce a un menor ringing en la puerta, un mayor rendimiento y un menor riesgo de fallo.

Existe más información de los encapsulados QDPAK y DDPAK en este enlace.