Una nueva serie de PoL de TDK, la µPOL, aprovecha un enfoque multidisciplinar para diseñar con una nueva tecnología de integración patentada, subiendo un peldaño en aspectos como la mejora de la densidad de potencia PoL, la reducción del tamaño (huella) y el aumento de beneficios del sistema.

Al ofrecer carriles de alimentación para FPGA y dispositivos similares, se requiere convertidores DC-DC de punto de carga (PoL).

Los diseños PoL tradicionales han empleado varios niveles de integración de componentes, pero básicamente ha sido un ensamblaje de componentes discretos.

Desarrollo del artículo sobre convertidores µPoL

En los actuales sistemas informáticos, los componentes más demandados son FPGA, CPU, ASIC, SoC y ahora los nuevos dispositivos ACAP (Adaptive Compute Acceleration Platform – Plataforma de Aceleración de Cómputo Adaptativa) que prometen un salto cuantitativo del rendimiento en aplicaciones como centros de datos, redes cableadas, 5G wireless, inteligencia artificial (IA) y sistemas avanzados de asistencia al conductor (ADAS) en el sector del automóvil.

Sin embargo, existe una “batalla” en curso entre el rendimiento / la velocidad de operación, el consumo de energía, el tamaño y las consideraciones prácticas de cómo ofrecer energía de manera eficiente a los elementos del circuito. Minimizar el consumo siempre ha sido una prioridad en la “lista de deseos” del diseñador de sistema, ya que conduce a la creación de dispositivos o sistemas de menores dimensiones para una subida de temperatura dada, permitiendo mejoras en densidad de encapsulado y funcionalidad, una expectativa esencial de los consumidores, así como un producto más ecológico.

En los dispositivos digitales, el gasto de energía está directamente relacionado con la oscilación de tensión, ya que las capacidades internas se cargan y descargan y la conmutación cada vez más rápida conlleva más transiciones por segundo y, por lo tanto, un mayor consumo. Para mitigar esto, las tensiones de alimentación para los dispositivos se han reducido continuamente desde los 5 V a menos de 1 V, mientras que, para optimizar el rendimiento, las subsecciones de los propios dispositivos ahora tienen carriles de alimentación separados, con un rango entre múltiples núcleos de procesador de 0,56 a 0,88 V con tecnología de 7 nm de próxima generación, una tensión similar para RAM de bloque, 1,35 o 1, 5 V para memoria DDR, 1,5 V para funciones auxiliares y 3,3 y 5 V para los requisitos de E/S legacy.

La integración SoC (system on chip) está impulsando tensiones adicionales para DSP, códecs y procesamiento de vídeo / gráficos. Incluso si las tensiones de la sección son similares, suelen necesitar estar generadas por separado para evitar interacciones no deseadas y, por lo tanto, se pueden habilitar separadamente y secuenciar su encendido / apagado.

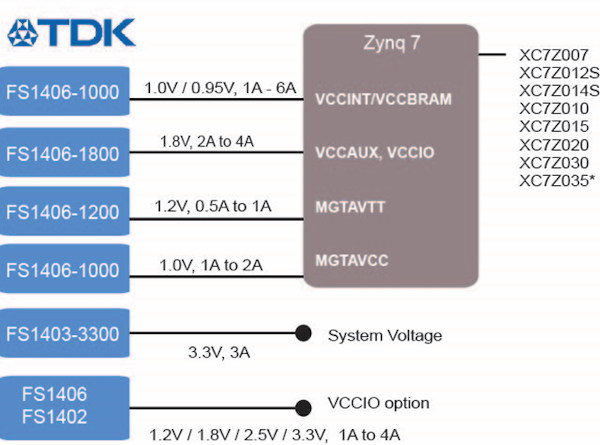

Tales bajas tensiones conllevan elevadas corrientes para una potencia dada, con algunos SoC, FPGA y núcleos procesadores en el rango de 4 A para consumir más de 200 A en su carril de alimentación principal, mientras que otros carriles en los dispositivos típicos requieren una corriente en el rango de 1 a 25 A para memoria, SERDES y voltajes E/S. Los reguladores PoL, por ellos mismos, se alimentan desde una tensión de bus superior, típicamente 5 o 12 V, a un nivel que las corrientes son muy inferiores para respetar el consumo de energía. Los diseñadores de sistemas generarán un diagrama de árbol de potencia para sintetizar la disposición (Figura 1).

Sin embargo, colocar los convertidores PoL cerca de dispositivos como FPGA plantea problemas: un FPGA típico en la gama Xilinx UltraScale tiene más de mil conexiones BGA y soporta dispositivos para E/S, así como un disipador de calor básico para las decenas de vatios producidas por el dispositivo.

Por lo tanto, el espacio se convierte en un elemento esencial en aplicaciones de pequeño formato (SFF) como tarjetas SoM FPGA y PCIe donde el nivel de potencia puede ser un inconveniente. El convertidor PoL ideal debe ser muy eficiente y tener un pequeño tamaño sin requisitos de disipador de calor y un bajo perfil, por lo que se puede montar en la parte trasera o incluso acoplarse bajo otros componentes como piggybacks montados en placa o subtarjetas. Por supuesto, también tiene que ofrecer una tensión precisa bajo condiciones estáticas y dinámicas, contar con un control de salida para cierre y secuenciado y estar protegido ante cortocircuitos, sobretensiones, subtensiones y estrés por elevación de temperatura.

Los dispositivos PoL modernos también disponen de características de comunicaciones, normalmente sobre un bus I²C usando PMBus, para establecer el dispositivo como un ajuste de una sola vez en los límites de detección de fallo o incluso “on-the-fly” para ajustes dinámicos de la tensión de salida en esquemas de ahorro de energía. El bus también puede indicar las condiciones PoL como corriente de carga, temperatura y estado para monitorización remota.

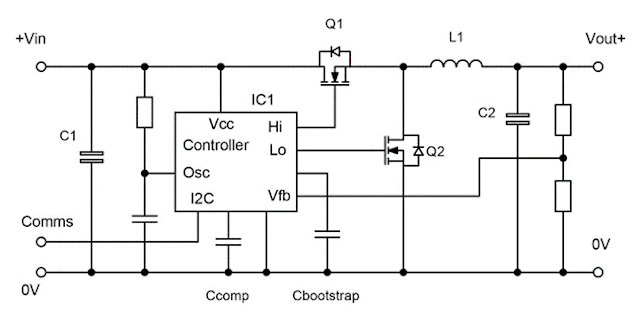

Topología PoL típica

El esquema básico de un convertidor PoL no aislado no ha cambiado durante muchos años (Figura 2). Las características como rectificación simultánea y conversión multifase con potencias superiores ahora son estándares, aunque existe alguna variación en los esquemas de control para optimizar el rendimiento dinámico. Los elementos comunes incluyen un interruptor “high-side” Q1 y un “low-side” Q2 que conmutan de manera alterna para suministrar la corriente de carga y “cargar” el inductor L1 en un periodo Q1 y descargar su energía a través de Q2 a la carga durante el periodo Q1. Un controlador IC1 muestra la salida y dirige Q1 y Q2 con señales moduladas por anchos de pulso complementarios para lograr la regulación de la tensión de salida por el efecto “averaging” de L1 y C2. IC1 también monitoriza y reacciona ante condiciones anormales e integra la función de comunicaciones externas.

Dimensionar los componentes y las condiciones operativas en un convertidor PoL es una situación intermedia; el inductor normalmente es el mayor componente y define el tamaño total. El inductor y el condensador de salida pueden tener menores dimensiones si el convertidor conmuta a frecuencias superiores, pero, al igual que en el FPGA, una conmutación más rápida de los MOSFET Q1 y Q2 provoca más disipación de potencia, demandando un componente de mayor tamaño a la hora de disipar el calor y mantener la subida de temperatura en los límites definidos.

Aquí, los avances en tecnología MOSFET para la resistencia-ON y la velocidad de conmutación han posibilitado mejoras en eficiencia y, ahora, las frecuencias en el rango de MHz son factibles.

Implementación de un PoL – la manera “antigua”

Los elementos PoL mostrados en la Figura 2 eran inicialmente componentes discretos que, en teoría, los diseñadores de tarjetas de sistemas podían situar en la placa madre. El diseño PoL es una mejora particular e, incluso, con información de aplicaciones del fabricante del controlador PWM resulta difícil lograr el rendimiento eléctrico óptimo cuando el PoL trabaja con otros componentes de la placa madre. Por lo tanto, también se ocupaba un espacio primordial.

Por esto, los fabricantes de convertidores PoL modulares han suministrado soluciones que son diseños probados para ofrecer la ventaja de un solo componente testado para la fuente, ahorrando al cliente los gastos de diseño y cualificación, así como la adquisición, el almacenamiento y la disposición de múltiples componentes discretos.

Los primeros módulos aportaban pocos beneficios porque ocupaban casi el mismo espacio que una solución discreta y eran igual de costosos, especialmente en elevados volúmenes de producción donde los costes fijos de una solución discreta podrían amortizarse.

Los módulos más recientes, por su parte, han integrado los componentes discretos en encapsulados de menor tamaño con algunos arreglos de apilado vertical para conseguir un ahorro de espacio real. Las versiones SIP ocupan poco espacio, pero suelen requerir una soldadura through-hole y no se pueden combinar con los diseños de productos de bajo perfil modernos.

También se encuentran disponibles algunos productos híbridos que sólo constan de los componentes de alimentación del convertidor PoL, dejando al usuario la capacidad de colocar el controlador en la placa madre, quizá en la parte posterior, lo que aporta un ahorro de espacio extra de gran utilidad.

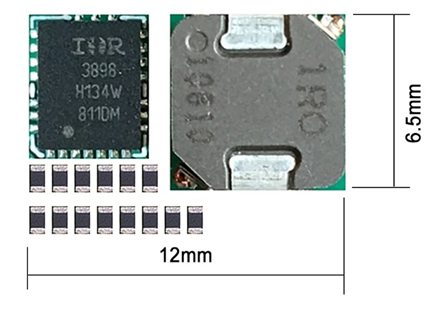

La Figura 3 muestra los componentes requeridos en una implementación discreta típica de una función PoL, que ocupa unos 50 mm² para una ratio de 6 A. Los condensadores de filtrado de entrada y salida de mayor tamaño no se incluyen y los conmutadores de MOSFET se integran en el controlador.

Implementación de un convertidor PoL – la próxima generación de tecnología embebida en un chip

Aunque las placas madre de “estilo antiguo” han “encogido” para adaptarse a plataformas con dimensiones mucho menores, como PCIe, tarjetas CoM, SSD, Edge e IA, el mercado está impaciente por encontrar soluciones más compactas para los circuitos de alimentación cada vez más necesarios. En las placas PCIe y CoM, por ejemplo, la sección de potencia puede ocupar hasta el 20 por ciento del espacio en la tarjeta.

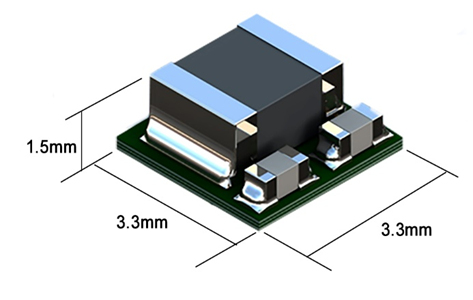

En lugar de utilizar los componentes discretos existentes y tratar de ensamblarlos de una manera diferente para conseguir mejoras en tamaño y rendimiento, TDK ha apostado por un enfoque de “borrado de pizarra” con el diseño de su nueva gama µPOL de PoL modulares, ofreciendo potencia para sistemas de 5 a 150 W (Figura 4). Se han combinado algunas tecnologías patentadas propias para lograr una impresionante reducción de tamaño al 25 por ciento menos que sus competidores, con una densidad de potencia cuatro veces mejor.

La serie FS140x, inicialmente disponible en versiones de 3, 4 y 6 A, se ampliará en el futuro a 25 y hasta 100 A. Los productos actualmente disponibles lo hacen en un encapsulado diminuto de 3,3 x 3,3 mm con una altura de 1,5 mm para cumplir los requisitos de lugares con restricciones de espacio como es el caso de la parte posterior de una placa madre o debajo de otros componentes como disipadores de calor y daughter boards. La densidad de potencia alcanzada se sitúa en 1 W / mm³, esto es 15 W en un espacio de 3,3 x 3,3 mm sin refrigeración por flujo de aire.

Al igual que el resto de PoL, los condensadores de entrada y salida externos necesitan añadirse para una implementación completa, pero son más compactos debido a la elevada frecuencia de conmutación empleada. Desde un punto de vista de sistema, parece mejor incorporar los condensadores externamente, ya que se pueden adaptar a los requisitos exactos de respuesta de transitorios de tensión y carga de la aplicación. De lo contrario, los condensadores de entrada y salida incluidos en un PoL tendrían que dimensionarse para la máxima carga posible, la máxima tensión de entrada posible y la tensión de salida ajustada, añadiendo un coste y un espacio de tarjeta innecesarios.

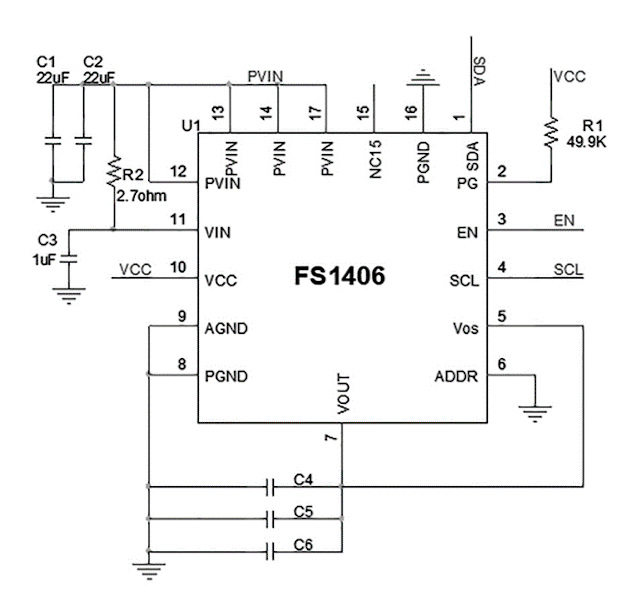

A diferencia de la solución PoL discreta de la Figura 3, con el TDK µPOL en una configuración mínima, aparte de los condensadores de entrada / salida, no se necesitan otros componentes como redes de compensación, resistencias de ajuste de salida, bootstrap o condensadores de desacoplo de pin.

Como parte esencial en la mejora alcanzada, aparecen la tecnología de inductor de película delgada de TDK, líder de la industria desde hace tiempo, y una nueva técnica SESUB o Semiconductor Embedded in SUBstrate que integra los MOSFET y los circuitos integrados de control en las capas de un sustrato de 250 µm de grosor con el inductor y dos condensadores de bypass de pequeño tamaño ubicados en la parte superior.

Otros aspectos clave son las técnicas de encapsulado: 1) sin wire bonds, haciendo que los dispositivos sean muy robustos en aplicaciones industriales, y 2) ligero, idóneo en drones, visión artificial y otras aplicaciones de pequeño formato (SFF).

Con una elevada eficiencia de diseño, TDK ha utilizado su experiencia en encapsulado para controlar las características térmicas y poder conducir el calor del CI y del inductor a las terminaciones de sustrato y a la placa madre. Esto es tan efectivo que, con una salida de 6 A, la temperatura del módulo solo sube hasta los +41 °C para un componente con entrada de 12 V y salida de 1,8 V. Aunque esto depende del flujo de calor a la placa madre, TDK ha demostrado que es posible ubicar múltiples µPOL con una separación de unos pocos milímetros, sin degradación en el ratio de potencia.

Beneficios del sistema µPOL

El tamaño diminuto del µPOL permite utilizar el mínimo espacio para la regulación de tensión cerca del dispositivo target y las aplicaciones son escalables, ya que los componentes de 3 a 6 A poseen las mismas dimensiones.

La tensión de salida se puede seleccionar entre 0,4 y 5 V, mientras que el rango de tensión de entrada oscila entre 4,5 y 16 V con una sola alimentación y entre 2,5 a 16 V con una fuente auxiliar extra que ofrece una tensión bias superior.

La funcionalidad de monitorización y control integrada en el µPOL también añade beneficios de sistema significativos: por ejemplo, cuentan con una salida “power good” y una entrada “enable” que se pueden utilizar para habilitar y deshabilitar la secuencia de salida de múltiples µPOL con los esquemas “radiométricos” y “simultáneos” disponibles. La protección es completa mediante el seguimiento de la sobretensión de salida, la subtensión de entrada y la sobrecarga de salida o el cortocircuito, con límites seleccionables y cierre de modo “hiccup”. Los dispositivos operan en el rango de -40 a +125 °C y tienen un cierre térmico programable con recuperación automática.

La interfaz I²C, que soporta modos Fast y Fast Plus, es compatible con una amplia variedad de parámetros a través de los comandos PMBus:

- Tensión de salida graduable de 0,4 a 5 V con resolución de 5 mV (versiones de entrada fija inicialmente disponibles – dependiendo de la variante)

- Recorte de tensión de salida (precisión inicial de ±0,5 por ciento)

- Ratios de arranque suave y parada opcionales de 0,5 o 1 mV/µs

- Límite PGood ajustable: 85, 90 y 95 por ciento de Vout

- Límite OVP ajustable: 105, 110, 115 y 120 por ciento de Vout

- Esquema OVP ajustable: abierto y cerrado

- Límite OCP ajustable: hasta 8 A con resolución de 250 mA

- Límite OTP ajustable: 75, 85, 125 y 145 °C

- Modos operativos “continuo” (CCM) o “discontinuo” (DCM) seleccionables para optimización de EMI y eficiencia

Con un amplio rango de dispositivos, opciones y parámetros, los diseñadores de sistemas pueden “mejorar” las aplicaciones utilizando el µPOL para minimizar el coste del mismo y maximizar la funcionalidad.

Ejemplo de aplicación

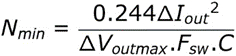

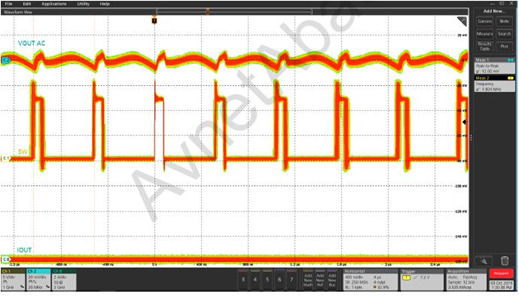

La Figura 6 muestra el TDK µPOL configurado para Vin = 12 V, Vout =1,8 V e Iout = 6 A con un requisito de tensión de rizado de menos de ±1 por ciento pp de Vout y existe una excursión máxima de ±3 por ciento de Vout con un paso de carga de 3 A. El componente µPOL FS1406 y dos condensadores de 22 µF han sido elegidos inicialmente para Cin y Cout. La frecuencia de conmutación Fsw es de 2 MHz.

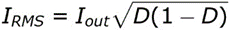

La selección del tipo de condensador de entrada depende de la gestión de corriente de rizado IRMS. En un convertidor buck que opera con un ciclo D, es dada por:

En esta aplicación Iout es 6 A y D = Vout/Vin = 0,15, dando un IRMS= 2.14A que se puede gestionar fácilmente mediante dos condensadores de 22 µF y 16 V TDK C3216X5R1C226M160AB.

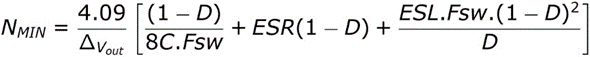

Para los condensadores de salida, existe un número mínimo requerido NMIN para poder cumplir el rizado target Δ Vout dado por:

Los condensadores MLCC TDK C2012X5R0J226K125AB tienen una ESR de 3 miliohmios, un ESL de 0,44 nH y una capacidad efectiva de 12 µF a 1,8 V. Resolviendo, el NMIN es 1,27 por lo que se asume que dos condensadores resultan adecuados.

El número mínimo de condensadores a la hora de cumplir la respuesta de transitorios de carga ΔVoutmax con un paso de carga ΔIout es dado por:

Resolviendo de nuevo con 12 µF, el NMIN es 0,4 y, por ende, dos condensadores C2012X5R0J226K125AB de TDK Corporation proporcionan una buena solución.

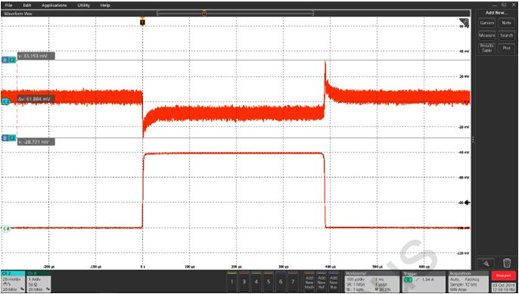

Los gráficos del rizado y la respuesta de transitorios de carga resultantes aparecen en las Figuras 7 y 8 que muestran una ondulación pp de solo 15,19 mV o el 0,8 por ciento, y una excursión de alrededor de 30 mV o ±1,7 por ciento con pasos de carga.

A tensiones de salida superiores, el número mínimo de condensadores de salida de 22 µF disminuye para cumplir la misma especificación de rizado y transitorios, con una salida de 2,25 V: solo se necesita uno.

El TDK µPOL – avances de rendimiento con soporte completo

Para soportar el diseño interno del µPOL, TDK ofrece un conjunto de herramientas que incluyen tarjetas de evaluación de propósitos generales con interfaces para acceso al bus I²C, con una GUI fácil de usar para configurar los componentes.

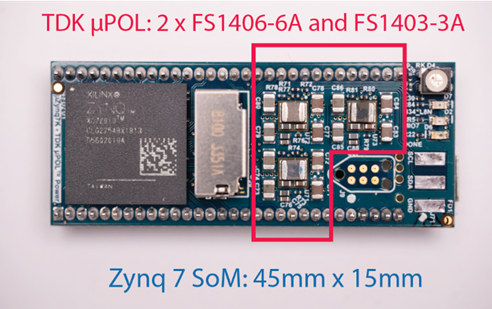

Además, las “‘Power Strip Design Boards” también se encuentran disponibles con hasta ocho unidades µPOL para alimentar todos los carriles, incluyendo las tarjetas secuenciadoras para Xilinx Spartan 7, Artix 7, Zynq 7, Zynq UltraScale+, Zynq UltraScale+ RFSoC, Versal ACAP (Versal Prime Series) y otros FPGA de fabricantes como Altera, NXP (i.Mx8, serie LS), Marvell/Cavium y Microsemi.

Y, para una implementación rápida, se suministran los esquemas junto a los “layout snippets” de PCB para los programas ORCAD/Allegro, Altium y Mentor PADs+/Xpedition CAD. Las soluciones de subsistemas de alimentación “ready to go” para los vendedores de FPGA se encuentran disponibles desde TDK y, como un miembro “Alliance Program Certified” de Xilinx, ha creado diseños de referencia completos para FPGA como la serie Zynq7.

Los componentes µPOL suponen un avance en densidad de potencia y reducción de tamaño para POL de hasta 6 A, con modelos de primer orden ofreciendo beneficios similares. Esta solución “plug and play” ahorra espacio y tiempo de diseño sin comprometer el rendimiento y, como un sistema en lugar de un componente, µPOL disminuye los requisitos de componentes externos y su espacio de tarjeta asociado y, por consiguiente, ahorra el coste total. La capacidad de programar el rendimiento sobre el bus I²C dota de flexibilidad de diseño y acorta el tiempo de llegada al mercado con el soporte de una excelente herramienta de diseño de TDK.

Para finalizar, el equipo paneuropeo de especialistas de electrónica de potencia de AVNET Abacus ofrece soporte local (en su mismo idioma) en cualquier fase del diseño de una aplicación. Para contactar y obtener más información, incluyendo fichas técnicas y vídeos, por favor, visite www.avnet-abacus.eu/tdk-micropol

Palabras clave: Punto de carga, PoL, convertidor DC-DC, eficiencia, tamaño, bajo perfil, FPGA, CPU, ASIC, SoC, ACAP, multinúcleo, CoM, SoM, Arquitectura de Potencia Intermedia, FS1406, FS1404, FS1403 y FS140x.