Walter Hagner, Product Sales Manager Digital/Wireless Central Europe, y Hao Wang, Product Manager Digital Central Europe de Rutronik nos explican el funcionamiento de los procesadores RISC-V de código abierto.

En respuesta a la estructura cada vez más compleja de los procesadores estándares, la Universidad de California en Berkeley creó hace diez años una arquitectura del conjunto de instrucciones abierta y altamente reducida.

Ahora está en su quinta generación – y ofrece muchas ventajas. Una de las razones para desarrollar un conjunto de instrucciones comparativamente simple fue investigar por qué la mayoría de los compiladores ni siquiera usa muchos de los modos de direccionamiento proporcionados por los procesadores comunes.

La nueva arquitectura del conjunto de instrucciones (ISA) se denominó RISC (Reduced Instruction Set Computer – conjunto de instrucciones reducidas) por su menor complejidad. La quinta versión (RISC-V), se basa en un enfoque de código abierto y parece ser un gran avance para RISC.

Uno de los principales motivos de esto es que la Fundación RISC-V, que ya tiene más de mil miembros y está impulsando el desarrollo de RISC-V ISA, no cobra tarifas de licencia por la utilización de los conjuntos de instrucciones. Incluso el uso comercial de RISC-V no requiere acuerdos de licencia ni pagos.

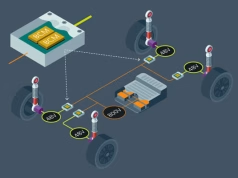

Esto hace que RISC-V sea una alternativa muy atractiva en comparación con las tecnologías de procesador x86 y ARM. Aparte de la reducción de costes significativa, también significa que los usuarios no se hacen dependientes de otras empresas. Cualquier persona puede desarrollar sus propios núcleos y procesadores RISC-V sin tener que “revelarlos”. En vista del hecho de que los procesadores también se pueden cargar como núcleos blandos en lógica programable, se trata de una ventaja que no se puede subestimar.

Flexibilidad y durabilidad con el código abierto

RISC-V define ISA, pero no la arquitectura de procesador. Esto dota a los desarrolladores de una gran flexibilidad, ya que pueden combinar RISC-V con cualquier arquitectura que deseen. Gracias al conjunto de instrucciones fijas, los programas desarrollados actualmente también se podrán ejecutar en implementaciones futuras. Esto hace que RISC-V sea particularmente interesante en aplicaciones industriales con ciclos de vida largos.

Todo el conjunto de instrucciones de RISC-V se fundamenta en formatos registro a registro, saltos condicionales e incondicionales, almacenamiento de datos, y constantes pequeñas y grandes. La arquitectura queda caracterizada por su variedad de registros, dado que RISC-V es una arquitectura de carga-almacenamiento que trabaja sin modos de direccionamiento complejos. Básicamente, tampoco tiene un área de E/S dedicada, sino solo E/S asignadas a la memoria.

Otro beneficio más del concepto RISC-V se encuentra en que no se necesita un microsecuenciador grande. Como tal, la mayoría de los comandos se ejecutan directamente por el hardware en lugar de por un microprograma. Esto tiene el efecto positivo de que generalmente sólo se requiere un ciclo de reloj.