Sondrel es una compañía conocida por diseñar chips digitales muy grandes y el secreto radica en su capacidad para garantizar que los datos fluyan alrededor del chip entre bloques utilizando una red en chip (NoC).

Sin un NoC, un chip podría necesitar hasta diez veces más memoria para funcionar de manera similar sin latencia, lo que sería antieconómico.

En un diseño ideal, todas las secciones que necesitan alta velocidad, por el alto flujo de datos entre ellas, estarían ubicadas lo más juntas posible, es decir, la memoria en el medio del chip junto a los bloques de IP (Propiedad Intelectual) que necesitan acceso a la memoria.

En realidad, además de la caché, la memoria se encuentra fuera del chip en chips de memoria dedicados, que utilizan tecnologías de memoria de última generación, de modo que los puntos de acceso a la memoria se encuentran en el perímetro del chip.

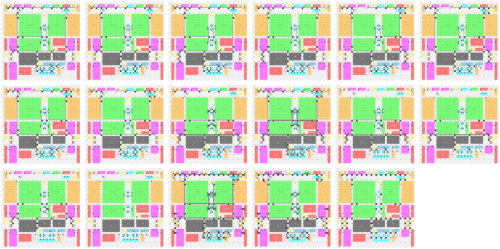

Como resultado, se necesita una red compleja de interconexiones para enrutar el tráfico de datos entre bloques y hacia y desde la memoria fuera del chip. En un diseño de chip grande, podría haber diecisiete capas de interconexiones horizontales más varias conexiones verticales entre estas capas.

“Es como diseñar un bloque de oficinas masivo de varios niveles donde hay que diseñarlo para permitir un movimiento óptimo de personas entre áreas y pisos”, explicó Anne-Françoise Brenton, experta en NoC de Sondrel.

Cuando muchas personas necesitan moverse rápidamente entre dos ubicaciones, se necesita un corredor amplio y rápido y su longitud afecta el momento en que llegan las personas. Del mismo modo, una ruta no urgente utilizada con poca frecuencia puede ser larga y estrecha y, por lo tanto, lenta. La analogía continúa con las interconexiones verticales que son ascensores con gran capacidad, ascensores que solo conectan dos pisos específicos para proporcionar una ruta dedicada para conexiones de alta velocidad y ascensores que se detienen en todos los pisos que son más lentos, pero conectan muchas ubicaciones. Además de esto, está el arbitraje que controla dinámicamente el flujo de datos a través del NoC con almacenamiento en búfer para suavizar y optimizar a medida que cambia la demanda, por ejemplo, cuando dos bloques de IP comparten y acceden a la misma memoria”.

Funcionamiento de un buen trabajo

El diseño del NoC es una colaboración iterativa a lo largo de todo el proceso de diseño de chips entre los equipos de diseñadores de front-end, back-end y NoC, ya que cualquier cambio puede tener un efecto en cadena en el trabajo del otro.

A medida que cristaliza el diseño frontal del diseño del chip, el requisito del NoC de arbitrar las demandas de carga se vuelve más claro, lo que hace al realizar un seguimiento de los datos y su ubicación en la memoria caché, fuera del chip o procesándose en un bloque de IP.

Uno de los desafíos en el diseño del NoC es que los bloques de IP de terceros pueden ser una solución de caja negra con muy pocos datos proporcionados sobre sus demandas de flujo de datos, ya que el proveedor desea proteger el funcionamiento exacto de su IP.

Esto se supera a medida que todo el diseño madura mediante el uso de análisis de tiempo para ayudar a garantizar que el NoC entregue los datos según lo requerido al arbitrar las vías para entregar los datos de acuerdo con las prioridades asignadas previamente; no puede haber cuellos de botella.

“El diseño de NoC es un acto de malabarismo en constante cambio”, concluyó Anne-Françoise Brenton. “Cambiar un parámetro y varias otras cosas podrían cambiar. Es tan intelectualmente desafiante como jugar varias partidas de ajedrez simultáneamente y es inmensamente gratificante”.