Pensado para su uso en dispositivos industriales, este diseño de referencia de puente para sensores de imagen permite compatibilizar salidas y entradas.

Lattice Semiconductor anuncia la disponibilidad de su nuevo diseño de referencia para aplicaciones de enlace de vídeo, en el cual utiliza la FPGA CrossLink de la misma marca.

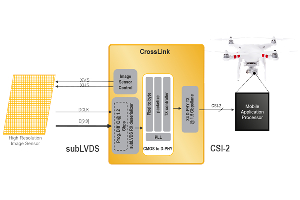

El SubLVDS to MIPI CSI-2 Image Sensor Bridge está dirigido a los diseñadores de dispositivos industriales, proporcionando una solución flexible y fácil de implementar para la conexión de procesadores de aplicación avanzados con muchos de los sensores de imagen utilizados actualmente en las aplicaciones de visión por computadora en entornos industriales.

Muchas de las aplicaciones de visión por computadora en entornos industriales utilizan sensores de imagen que poseen interfaz SubLVDS, la cual es incompatible con la interfaz MIPI CSI-2 D-PHY empleada en los actuales APs. No obstante, muchos integradores OEM de dispositivos industriales buscan implementar estos APs en sistemas de visión por computadora existentes.

Este diseño de referencia para sensores de imagen de Lattice permite a los diseñadores crear soluciones de bridging de una forma fácil y rápida, de forma que un AP con una interfaz MIPI CSI-2 puede conectar con un sensor de imagen SubLVDS.

Además, el nuevo diseño se proporciona de forma gratuita para demostrar el uso de las IPs modulares CrossLink de Lattice, incluyendo el conversor de píxel a byte, el receptor de sensor de imagen SubLVDS, y un transmisor CSI-2/DSI D-PHY.

Complementos para este diseño de referencia

La compañía fabricante también proporciona un diseño completo de FPGA basada en GUI de fácil uso, y un entorno de verificación de software, el software de diseño Diamond, para simplificar y acelerar el desarrollo de dispositivos.

Proporciona un ancho de banda de hasta 1,2 Gbps por cada línea de entrada, con un ancho de banda de hasta 1,5 Gbps para cada línea de salida, configuración de parámetro dinámico vía I2C, y soporte opcional para recorte de imágenes (cropping). También presenta 4, 6, 8 o 10 líneas de entrada SubLVDS a 1, 2 o 4 líneas de salida MIPI CSI-2.