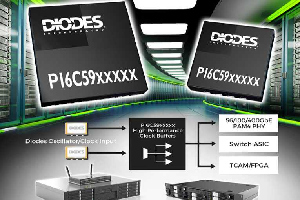

Los nuevos búferes de reloj diferenciales para comunicaciones terabit, modelos PI6C59xxxxx, son idóneos en centros de datos y estaciones base 5G.

Diodes anuncia la serie PI6C59xxxxx de búferes de reloj diferenciales, que soporta velocidades Ethernet de hasta400 Gbit/s y está especialmente indicada en aplicaciones de alto rendimiento como centros de datos y estaciones base 5G, donde se necesita aumentar la densidad de potencia, el rendimiento, el ancho de banda y la funcionalidad.

Ante la creciente demanda de redes que operen con una velocidad de 25 a 400 Gbit/s (conocida como Terabit Ethernet o TbE), los diseñadores de switches y routers están sometidos a la presión de mantener la integridad de señal. La serie PI6C59xxxxx de búferes de relojes diferenciales aporta un mejor margen de señal y, al mismo tiempo, amplía la capacidad de dirigir todas las señales de reloj y datos usadas en comunicaciones de alta velocidad. Cubre un amplio número de velocidades y tecnologías, así como de combinaciones en configuraciones de entrada y salida.

Los nuevos dispositivos PI6C59xxxxx han sido desarrollados con la misión de incrementar la dispersión de las fuentes de sincronización y mejorar la distribución de reloj y datos en aplicaciones de 1,5 a 6 GHz, abarcando 25G, 40G, 56G, 100G y 400GbE. Aquí se requiere elevada estabilidad y rapidez en los tiempos de caída / subida. El jitter de sólo 10 fs permite cumplir los objetivos de estabilidad y precisión.

Posibilidades en los búferes de reloj anunciados

Todos estos búferes de relojes diferenciales para comunicaciones terabit se suministran en un encapsulado TQFN con entre dieciséis y cuarenta y ocho pines, que ofrece buena conductividad térmica en un formato compacto.

Con trece variantes, esta serie soporta las principales tecnologías de señalización usadas en redes de alta velocidad, incluyendo lógica de modo de corriente (CML), señal diferencial de bajo voltaje (LVDS), lógica positiva de emisor acoplado de baja tensión (LVPECL) y SSTL, así como LVCMOS. Entre las posibles configuraciones se encuentran dos, cuatro, doce y dieciséis salidas para búferes de dispersión y de datos / reloj.