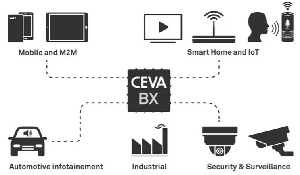

CEVA ha anunciado su nuevo procesador de señales híbrido CEVA-BX, pensado para su uso como controlador de arquitectura para el procesamiento de señal digital, y controlador de señal digital en dispositivos del Internet de las cosas (IoT).

Este dispositivo permite trabajar con nuevos algoritmos para el procesado de señal digital en aplicaciones de voz, vídeo, comunicaciones, sensorización, y para el control de señal digital, ofreciendo capacidades DSP de propósito general, las cuales son necesarias para el control motor y la electrificación.

La arquitectura del procesador de señales híbrido CEVA-BX permite extender el alcance de mercado de CEVA a los sectores industrial y automotriz actualmente en crecimiento, y que hoy por hoy no se encuentran bien atendidos por DSPs legacy o MPU/MCUs con coprocesadores DSP de bajo rendimiento.

Pensado para sobrepasar las arquitecturas de propósito especial como los DSPs de audio o los MCUs con extensiones DSP, este procesador de señales híbrido ofrece una arquitectura de procesador moderna con un alto nivel de programación.

Tecnología en el procesador de señales híbrido

Este nuevo DSP (Digital Signal Processor) híbrido de CEVA ofrece una arquitectura DSP renovada, combinando los requisitos de bajo consumo inherentes a los núcleos DSP con una programación de alto nivel y unos requisitos de tamaño de código pequeño para una amplia base de control de código.

Utiliza una pipeline de once etapas y una microarquitectura VLIW de cinco vías, ofreciendo procesamiento paralelo con motores de computación de doble escala, carga y almacenamiento, y control de programa que alcanza la velocidad de 2 GHz con un nodo de procesamiento TSMC de 7 nanómetros, empleando células estándares comunes y compiladores de memoria.

El ISA (Instruction Set Architecture) del CEVA-BX incluye soporte para SIMD (Single Instruction Multiple Data), ampliamente utilizado en tareas de inferencia en redes neuronales, reducción de sonido y cancelación de eco, así como unidades de punto flotante con precisión half, single y double para fusión de alta precisión y algoritmos de posicionamiento.

El dispositivo utiliza en su arquitectura los principios de las arquitecturas de los microprocesadores avanzados, como el gran conjunto de registro ortogonal de propósito general para maximizar la eficiencia del compilador de C, el innovador BTB (Branch Target Buffer) para minimizar la sobrecarga de la rama, hardware loop buffer para consumo energético reducido, subsistema de memoria totalmente cacheado, y soporte nativo para todos los tipos estándares de C.

El dispositivo utiliza en su arquitectura los principios de las arquitecturas de los microprocesadores avanzados, como el gran conjunto de registro ortogonal de propósito general para maximizar la eficiencia del compilador de C, el innovador BTB (Branch Target Buffer) para minimizar la sobrecarga de la rama, hardware loop buffer para consumo energético reducido, subsistema de memoria totalmente cacheado, y soporte nativo para todos los tipos estándares de C.

Su puntuación CoreMark/MHz es de 4,5, reflejando sus capacidades de control de la arquitectura.

El CEVA-BX se encontrará disponible a partir del fin del primer trimestre de este año para licenciamiento general.