En este artículo, Martin Motz, Product Sales Manager CPU de la compañía Rutronik, explica cómo trabajan las tecnologías incorporadas en el microcontrolador Intel Quark SE (Atlas Peak) y dónde proporcionan los mayores beneficios. Caracterizándose por la tecnología de búsqueda de patrones y un hub de sensor, el nuevo microcontrolador amplía las redes IoT en todo el camino hacia sus extremos inteligentes. Es el primer paso hacia el Edge IoT.

La tecnología de búsqueda de patrones posee una matriz neuronal que clasifica contenido mediante la comparación directa con patrones existentes. La matriz es una potente memoria asociativa y “paralelizada” (Content Addressable Memory – CAM – Memoria de Contenido Direccionable) que no se vincula a un core de CPU (adicional) – ni a un conjunto de comando o compilador. La IP de hardware integrada – un bloque de función Intel especial – se basa en una red de unidades procesadoras paralelas – las neuronas – a la hora de implementar algoritmos KNN y RBF (K-Nearest Neighbor – K-vecinos más cercanos y Radial Basis Function – Redes de función de base radial).

El core procesador del microcontrolador Intel Quark SE es compatible con el Pentium 586 ISA, lo que implica que dispone de un conjunto de comando compatible con los anteriores Pentium.

Trabajando con memoria asociativa

En sistemas de memoria convencionales, el direccionamiento mediante direcciones explícitas refleja con regularidad una estructura; las posiciones de memoria definidas como un resultado se asignan inicialmente como un valor «en blanco». La programación se fundamenta en reglas. Por otro lado, la memoria asociativa, como indica su nombre, usa la asociación para acceder a contenidos individuales. Su organización estructural resulta independiente de la operación de acceso. En la memoria asociativa “idealizada”, las posiciones de memoria sólo se crean donde ha tenido lugar previamente una operación de escritura. Se accede al contenido mediante la entrada de un valor de memoria, no vía dirección de memoria.

La implementación de grandes memorias asociativas es difícil porque incluso las entradas imprecisas están destinadas a lograr el resultado deseado. Esto se puede conseguir con redes neuronales. La clave del éxito – es decir, el procesamiento correcto de un patrón – consiste en un entrenamiento de la red neuronal, y la tecnología de búsqueda de patrones del Intel Quark SE permite hacerlo.

Búsqueda de patrones en el microcontrolador Intel Quark SE

El bloque de función de búsqueda de patrones Intel posibilita un análisis de escenario junto a una nueva técnica de procesamiento previo de señal de alta eficiencia. De esta forma, los escenarios complejos se pueden comprobar con más rapidez y precisión que con programación de software convencional. De hecho, dependiendo del perfil de aplicación, esta solución suele ser más fácil de implementar y, por consiguiente, crea nuevas posibilidades de uso.

El bloque de búsqueda de patrones del Intel Quark SE forma una matriz reconfigurable dinámicamente. Al abandonar la programación basada en reglas complejas, cuenta con la facultad de reconfigurar contenido, para auto-aprendizaje y convergencias sucesivas. Se puede “entrenar”, por lo que es capaz de clasificar cualquier tipo de datos. En el proceso, las nuevas entradas de datos se comparan con los datos “memorizados” en la MCU y se identifica el mejor patrón.

La tecnología integrada de búsqueda de patrones en el microcontrolador Intel Quark SE aporta numerosas ventajas sobre la programación convencional basada en reglas:

- Método estandarizado y desarrollo de algoritmo automatizado

- Análisis adaptable que permite formación y profundización continuas

- Tiempo de búsqueda constante por paso, sin importar los volúmenes de datos

- Periodos de desarrollo de algoritmos más cortos, lo que conlleva un menor tiempo de llegada al mercado

El potencial de esta tecnología de búsqueda de patrones se puede explotar todavía más en aplicaciones muy complejas.

Hub de sensor en el nuevo procesador

Otra nueva característica del microcontrolador Intel Quark SE es la integración de un hub de sensor, que analiza con regularidad las señales de entrada de sensor y, posteriormente, se emplea para buscar patrones con el objetivo de clasificar el reconocimiento de gestos y actividad. Gracias a la inteligencia de las inmediaciones de los sensores y los dispositivos terminales, se reducen los volúmenes de datos de la red. Esto también minimiza la carga de las capacidades de gateway y, en consecuencia, ahorra costes de ancho de banda.

La unidad funcional integrada ayuda a optimizar el consumo de energía al procesar señales wake-up programables. Al basarse en el modo sleep de CPU, se consigue una considerable mejora en eficiencia, así como una extensión de la vida de la batería, especialmente cuando se revisan con frecuencia múltiples señales de entrada de sensor en modo Always Listening.

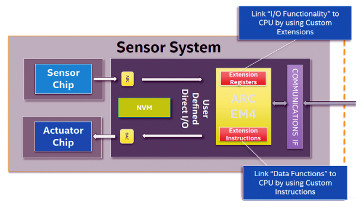

El subsistema de sensor es una solución que incorpora hardware y software para tareas de control en el procesamiento de señales de entrada analógicas y digitales. Esto mitiga la carga en el procesador host y el procesamiento de datos de sensor en modo Low Power relativo al procesador host. El procesador de 32 bit requerido para este propósito – un procesador de señal digital ARC EM4 DSP – cuenta con bloques de función acoplados estrechamente para beneficiarse de un acceso con mínimo tiempo de latencia. El subsistema de sensor se compone de una serie de comandos específicos Intel para fracciones, procesamiento de números complejos, generación de funciones de seno / coseno y unidades de coma flotante (FPU). El acceso se ofrece a una caché de instrucción 8 KB L1 y a una memoria de 8 kB Data CCM (Closely Coupled Memory – memoria acoplada al núcleo).

Para la conexión de sensor, existe acceso a conversión de analógico a digital de 12-bit con hasta 19 canales, así como 16 puertos GPIO. Las conexiones de bus de datos serie empleadas son 2 x I2C Master (Estándar / FM) y 2 x SPI Master (velocidad de reloj de 16 MHz con 4 elecciones de chip).

También se encuentra disponible un compilador separado que genera un archivo binario para el subsistema de sensor. Un compilador basado en GCC de código abierto con plugin Eclipse de GitHub y un IDE Designware de Synopsys se convierte en una opción para ello.

Tanto el hub de sensor como la tecnología de búsqueda de patrones en el microcontrolador Intel Quark SE se implementan como una solución de hardware totalmente integrada, evitando así incurrir en costes de adquisición de componentes adicionales.

Siga leyendo en Áreas de aplicación para el microcontrolador Intel Quark SE