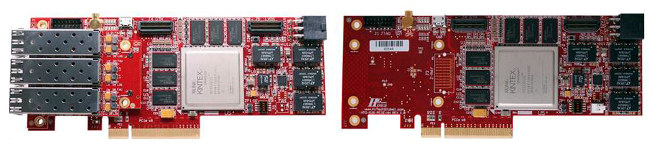

HiTech Global ha presentado su nueva placa de desarrollo en formato PCI Half Size Xilinx Kintex UltraScale HTG-K816 en formato PCI Half Size.

HiTech Global ha presentado su nueva placa de desarrollo en formato PCI Half Size Xilinx Kintex UltraScale HTG-K816 en formato PCI Half Size.

Esta placa está equipada con el FPGA Xilinx Kintex UltraScale 035, 040, o bien 060, proporcionando acceso a ocho líneas de PCI Express de tercera generación (8x8G), contando con dos bancos independientes de componentes de memoria DDR4 de 72 bits (hasta 5 GB), y una interfaz de panel Z-Ray que encontramos en el panel frontal y que nos permite alojar tarjetas intermedias (mezzanine cards) de alta velocidad.

El puerto Z-Ray en la nueva placa de desarrollo en formato PCI Half Size está equipado con hasta dieciséis transceptores serie GTH (16×16,3G) en la placa FPGA, junto a la alimentación (que es de 12V/5A, 3.3V/16A, y VCCIO/1A), el reloj diferencial, y las señales de control (single-ended y entradas/salidas I2C).

El uso de la interfaz Z-Ray en esta placa de desarrollo en formato PCI Half Size viene dado porque ocupa un área pequeña, ofreciendo el mayor rendimiento y la mejor integridad de la señal para un gran número de transceptores serie trabajando a una velocidad de hasta 28 Gbps.

También proporciona la mejor solución mecánica con una interfaz adaptable a diferentes alturas. HiTech ha desarrollado un portal en línea dedicado específicamente a dar a conocer el desarrollo de tarjetas para la interfaz Z-Ray, de forma que los partners puedan disponer de toda la información y herramientas necesarias.

Las interfaces intermedias (mezzanine) Z-Ray son soportadas por una serie de tarjetas auxiliares off-the-shelf como, por ejemplo, Hybrid Memory Cube (HMC), QSFP+, SFP+, FireFly, QSFP28 (gearbox), y CFP4 (gearbox).

Complementos a la placa de desarrollo en formato PCI Half Size

HiTech Global también ofrece servicios de diseño para la realización de cualquier módulo que requiera acceso a la interfaz Z-Ray y a los transceptores serie GTH en el FPGA que viene montado en la placa.

Las pequeñas dimensiones de la plataforma facilitan la creación de grandes clústeres de computación optimizando el espacio, un bien siempre necesario y escaso en los centros de proceso de datos.